## UN METODO EFFICIENTE ED AUTOMATICO PER CARATTERIZZAZIONI DELL'INTEGRITA' DI SEGNALE IN BUS MULTICONDUTTORE COMPLESSI

Piero Triverio, Alessandro Chinea, Stefano Grivet-Talocia, Haisheng Hu

Dipartimento di Elettronica, Corso Duca degli Abruzzi 24, 10129 Torino, Italia

L'integrità dei segnali nei moderni sistemi digitali è uno dei fattori più importanti per la loro affidabilità. In assenza di meccanismi di correzione degli errori, poco comuni nei bus interni, un eventuale errore di trasmissione può avere conseguenze drammatiche sulla performance e sulla stabilità funzionale dell'intero sistema. Questa evenienza va prevenuta con un attento progetto dei bus di comunicazione che analizzi accuratamente tutti i possibili meccanismi di distorsione dell'informazione trasmessa, come diafonia, attenuazione, dispersione, riflessioni multiple [1]. Queste analisi vengono tipicamente effettuate tramite il calcolo di diagrammi ad occhio [8] e richiedono modelli efficienti e a larga banda dell'intero bus. Questo articolo illustra un metodo sistematico per costruire questi modelli.

Il primo passo del metodo proposto è la caratterizzazione del bus tramite la sua matrice scattering, calcolata con una simulazione di campo elettromagnetico o misurata con un analizzatore di reti vettoriale. Successivamente, viene costruito un circuito equivalente la cui matrice scattering S(s) approssima i campioni nel senso dei minimi quadrati. Questo approccio indiretto ha il vantaggio di fornire un modello del bus compatibile con qualunque simulatore circuitale e di non risentire dei problemi di aliasing legati all'uso della FFT per convertire i campioni dal dominio della frequenza a quello del tempo. L'algoritmo Vector Fitting [2] è il metodo più utilizzato per estrarre questo circuito equivalente. L'efficienza del circuito concentrato decresce però all'aumentare della lunghezza elettrica del sistema, per via dell'elevato numero di elementi necessari per approssimare i crescenti ritardi di propagazione [5-7]. Per ovviare a questo problema sono state perciò proposte alcune generalizzazioni dell'algoritmo Vector Fitting [5-8] in grado di generare un modello circuitale distribuito che includa linee di trasmissione ideali adatte a rappresentare efficacemente i ritardi di propagazione. Il calcolo dei coefficienti del modello viene effettuato in due fasi. Nella prima vengono stimati i ritardi di propagazione direttamente dai parametri scattering campionati, tramite la trasformata di Gabor [5] o l'analisi della risposta del sistema ad un impulso a banda limitata [8]. L'identificazione dei poli e dei residui della parte razionale della funzione di trasferimento S(s) avviene quindi con un metodo iterativo analogo al Vector Fitting [7]. Un passo importante per garantire la stabilità delle simulazioni di transitorio è la verifica e l'imposizione della passività del modello ottenuto. Si può infatti dimostrare che, quando questa proprietà è violata, il modello puo' far divergere le simulazioni di transitorio [3,4], oltre ad essere fisicamente inconsistente con il componente reale, per natura passivo. La passività di modelli con ritardi può essere controllata e imposta perturbando gli autovalori di un'opportuna matrice Hamiltoniana [8] o i valori singolari della matrice scattering [8,9].

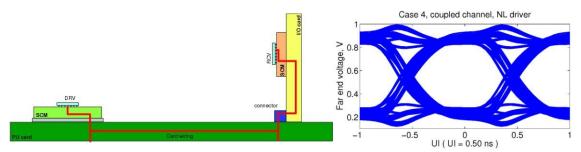

La procedura descritta è stata testata su quattro bus di comunicazione [8] che collegano le schede di un sistema di calcolo di alta gamma (si ringrazia IBM Deutschland Research & Development GmbH per aver fornito gli esempi di applicazione). Per ognuno dei quattro bus sono stati presi in esame nove canali: uno centrale designato come "vittima" e gli otto più prossimi ad esso designati come aggressori. La Figura 1 mostra una delle quattro

configurazioni analizzate, tutte composte da un'articolata sequenza di linee multiconduttore, connettori, package e moduli multichip. I tempi di identificazione del modello e di imposizione della passività testimoniano il ridotto costo computazionale del metodo, che fornisce il circuito equivalente in un tempo compreso tra 5 e 15 minuti circa, nonostante il numero elevato di porte del sistema (18). Ancora più interessanti sono i tempi di calcolo del diagramma da occhio, generato applicando una sequenza pseudocasuale di 1000 bit alla linea "vittima" ed un segnale di clock ad ogni linea "aggressore". Nonostante la complessità della struttura, il diagramma viene calcolato in meno di un minuto per il singolo canale e in circa un'ora per i nove canali accoppiati [8], nonostante siano utilizzati modelli realistici non lineari e dinamici per le terminazioni (drivers e receivers).

Figura 1 - Geometria del bus multiconduttore tra un nodo di elaborazione e una scheda di I/O, e relativo diagramma ad occhio. La simulazione tiene conto di tutti i 9 canali accoppiati.

| Tipo di canale        | Identificatione<br>modello | Imposizione<br>passivita' | Diagramma occhio singolo canale | Diagramma occhio canali accoppiati |

|-----------------------|----------------------------|---------------------------|---------------------------------|------------------------------------|

| Nodo-scheda i/o       | 277 s                      | non necessaria            | 51 s                            | 53m 34s                            |

| Internodo (backplane) | 377 s                      | 352 s                     | 53 s                            | 41m 58s                            |

| Internodo (flexfoil)  | 87 s                       | 322 s                     | 53 s                            | 61m 54s                            |

| Intranodo             | 167 s                      | 656 s                     | 47 s                            | 52m 13s                            |

Tabella 1 - Tempo di calcolo necessario per costruire i macromodelli delle varie strutture, imporne la passività e calcolare il diagramma ad occhio relativo ad un singolo canale e a 9 canali accoppiati (1000 bit). Le simulazioni sono state eseguite con IBM PowerSpice [8].

## Bibliografia

- [1] R. Achar and M. Nakhla, "Simulation of High-Speed Interconnects", *Proceedings of The IEEE*, Vol. 89, pp. 693-728, May 2001.

- [2] B. Gustavsen and A. Semlyen, "Rational approximation of frequency domain responses by vector fitting", IEEE Trans. Power Delivery, vol. 14, no. 3, pp. 1052-1061, July 1999.

- [3] P. Triverio, S. Grivet-Talocia, M. S. Nakhla, F. Canavero, R. Achar, "Stability, causality, and passivity in electrical interconnect models," *IEEE Trans. Adv. Packag.*, vol. 30, no. 4, pp. 795–808, 2007.

- [4] S. Grivet-Talocia, "On Driving Non-passive Macromodels to Instability", International Journal of Circuit Theory and Applications, vol. 37, n. 8, pp. 863-886, October, 2009.

- [5] S. Grivet-Talocia, "Delay-Based Macromodels for Long Interconnects via Time-Frequency Decomposition", *IEEE 15th Topical Meeting on Electr. Perf. of Electr. Pack.*, Scottsdale (AR), USA, pp. 199-202, Oct. 23-25, 2006.

- [6] A. Charest, D. Saraswat, M. Nakhla, R. Achar and N. Soveiko, "Compact Macromodeling of Long Delay Interconnects via Delayed Rational Functions", IEEE Microwave and Wireless Components Letters, Volume 17, Issue 12, pp. 828 830, Dec. 2007.

- [7] A. Chinea, P. Triverio, S. Grivet-Talocia, "Delay-based macromodeling of long interconnects from frequency-domain terminal responses," IEEE Trans. on Advanced Packaging.,v.33, no.1, pp.246-256, 2010.

- [8] A. Chinea, S. Grivet-Talocia, H. Hu, P. Triverio, D. Kaller, C. Siviero, M. Kindscher, "Signal integrity verification of multi-chip links using passive channel macromodels," IEEE Trans. on Advanced Packaging, 2010. (in press).

- [9] A. Chinea, S. Grivet-Talocia, P. Triverio, "On the Performance of Weighting Schemes for Passivity Enforcement of Delayed Rational Macromodels of long Interconnects", Proc. of 18th IEEE *Topical Meeting on Electr. Perf. of Electr. Pack. and Syst.*, Tigard (OR), USA, pp. 61-64, October 19-21, 2009